AppleのM1チップやニューラルネットアクセラレータなど、大手IT企業をはじめ世界的に開発が進められているのが独自設計プロセッサや領域特化型プロセッサです.

ユーザの望む処理に最適化したハードウェアは高速かつ低消費電力性に非常に優れています.しかしその設計のためにはハードウェアに関する高度な知識・技術と,検証用に高いコストをかけハードウェアを試作する必要がありソフトウェア技術者のみでの開発は困難でした.

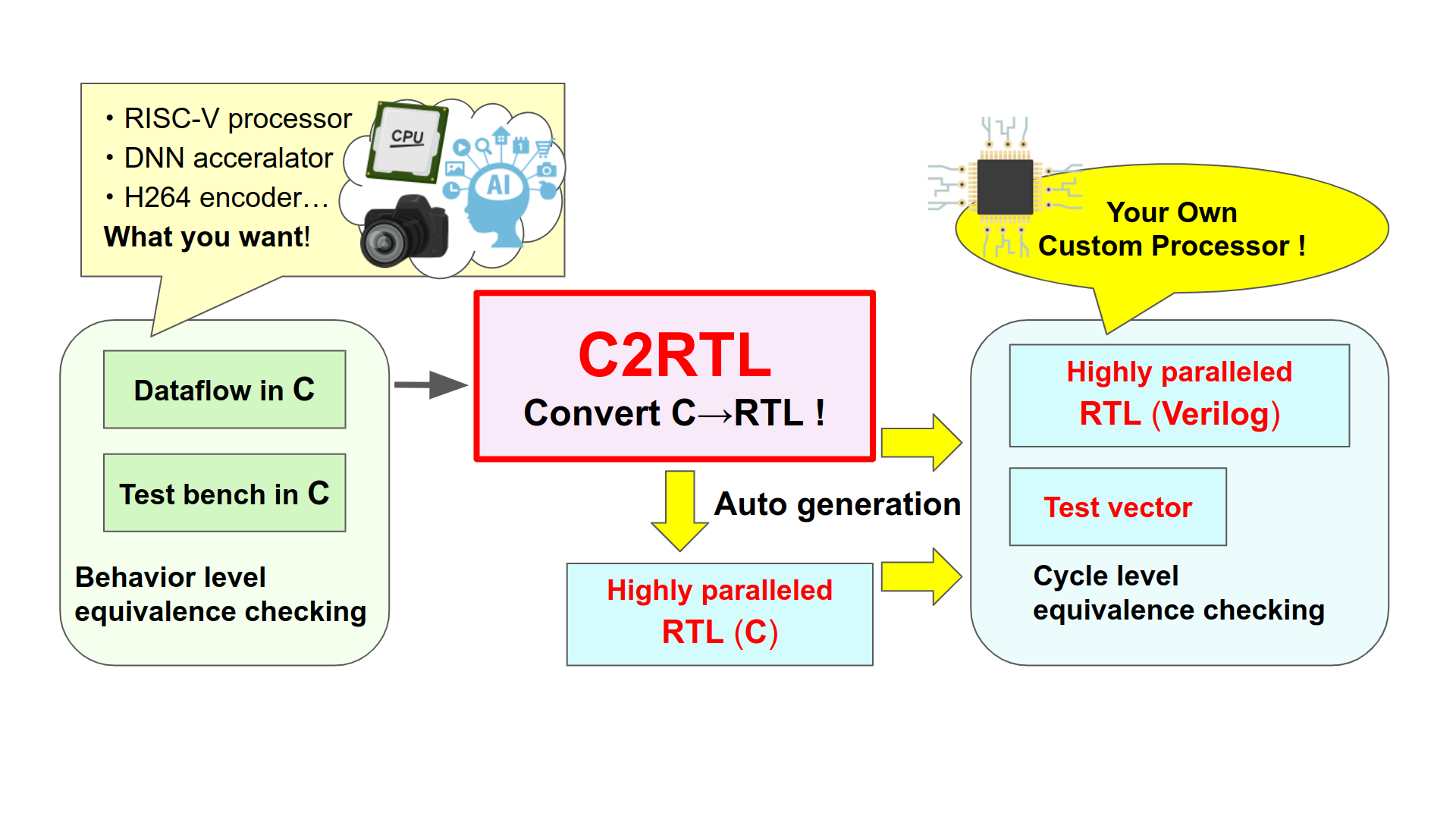

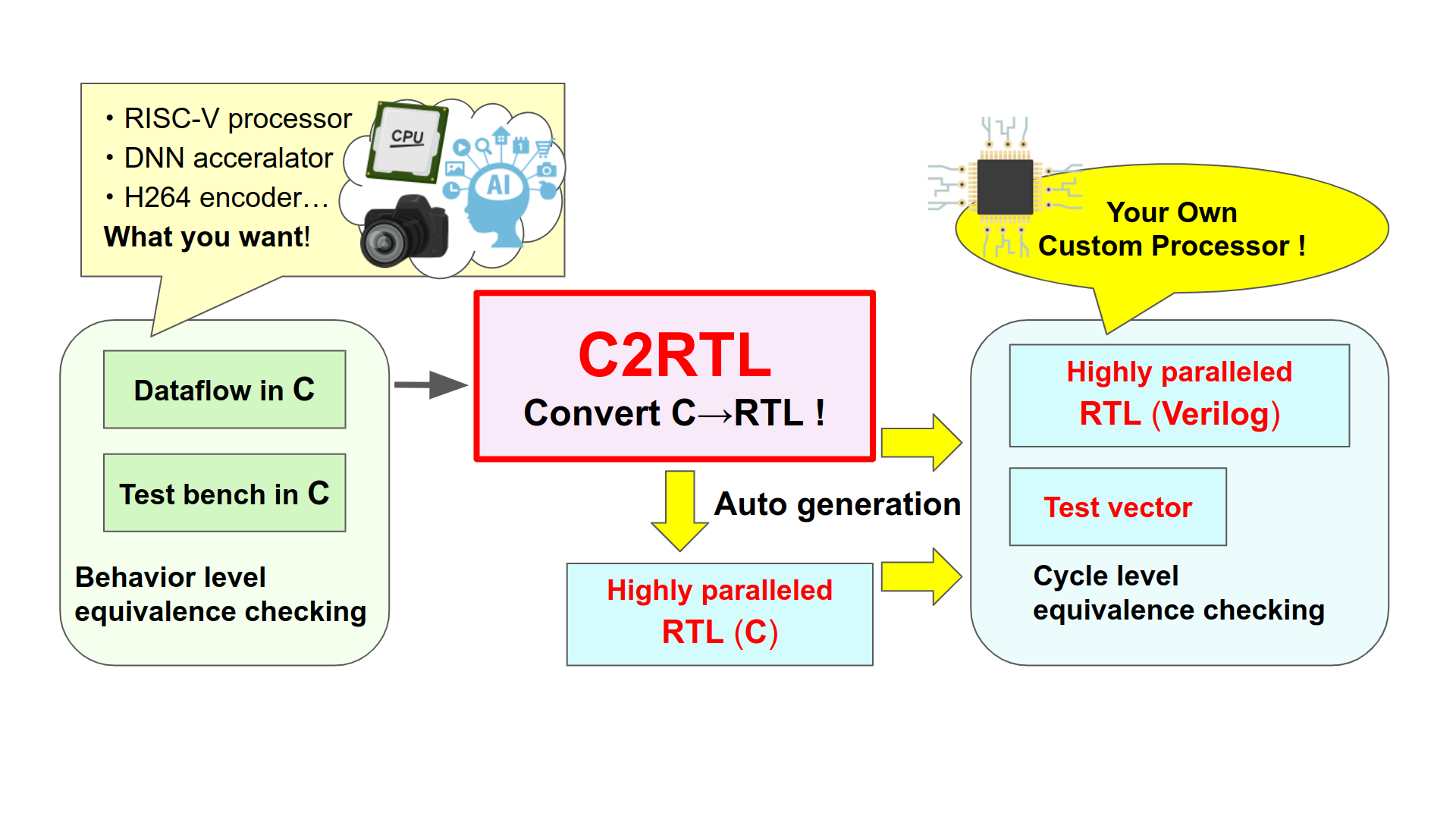

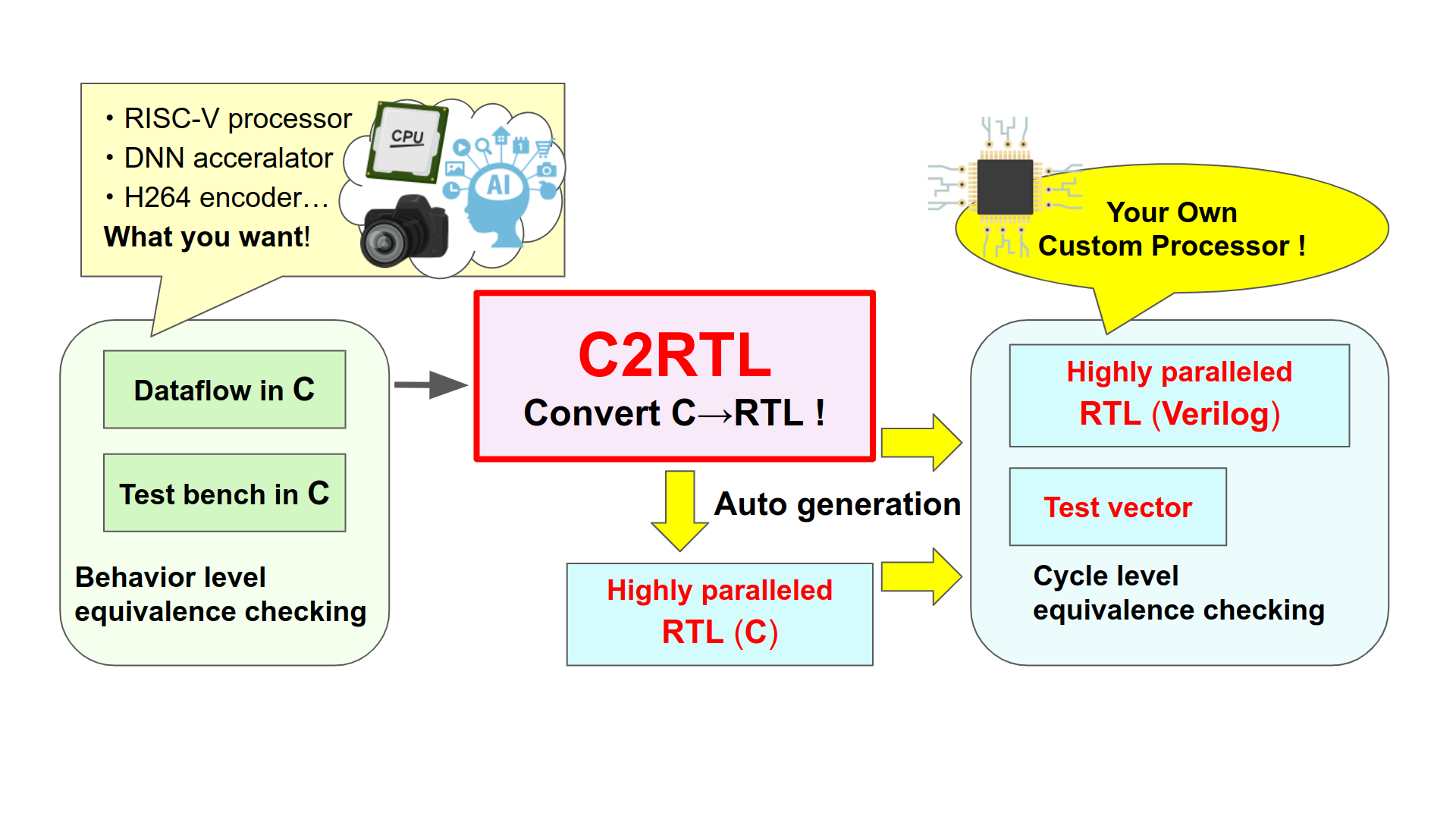

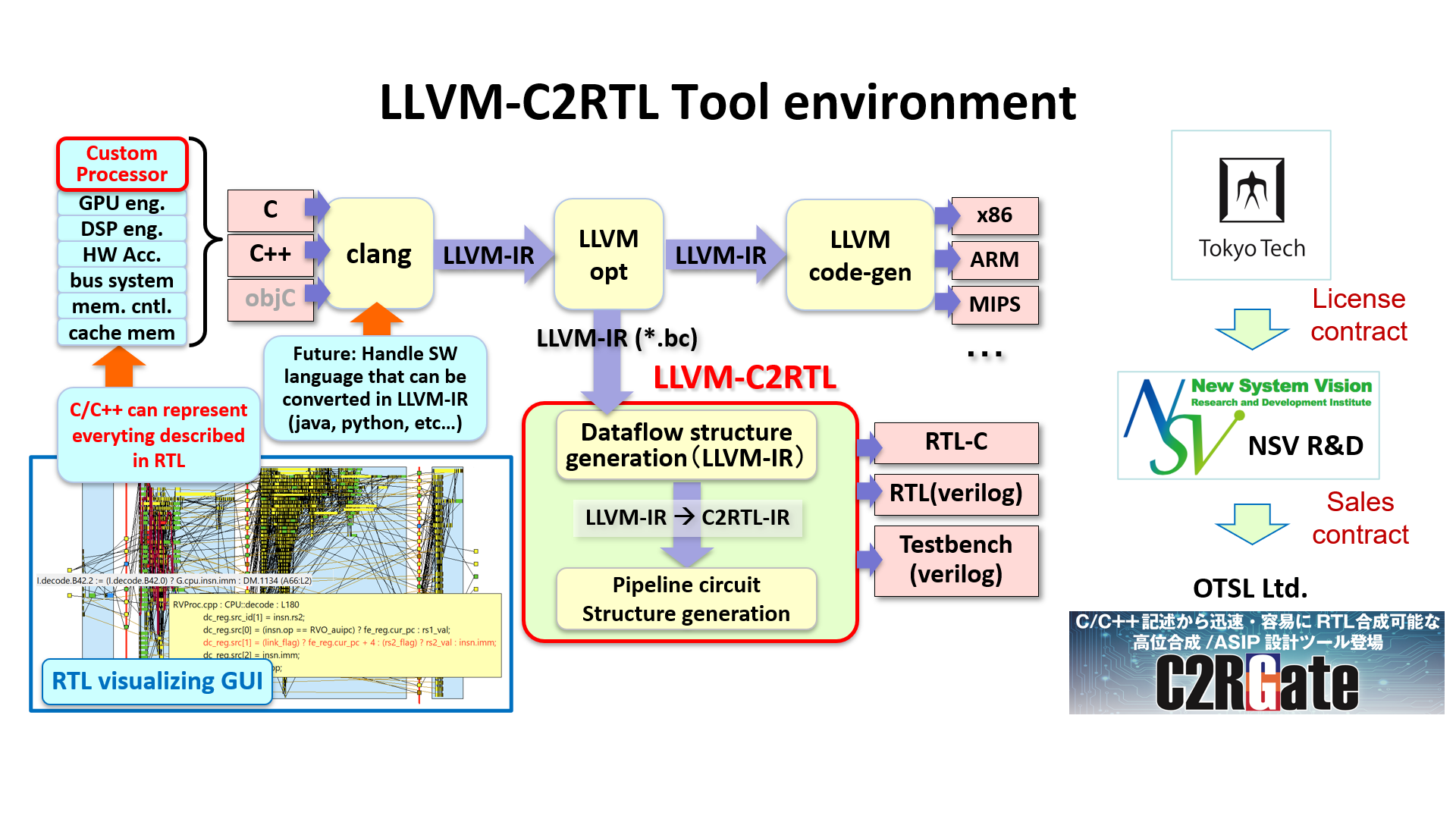

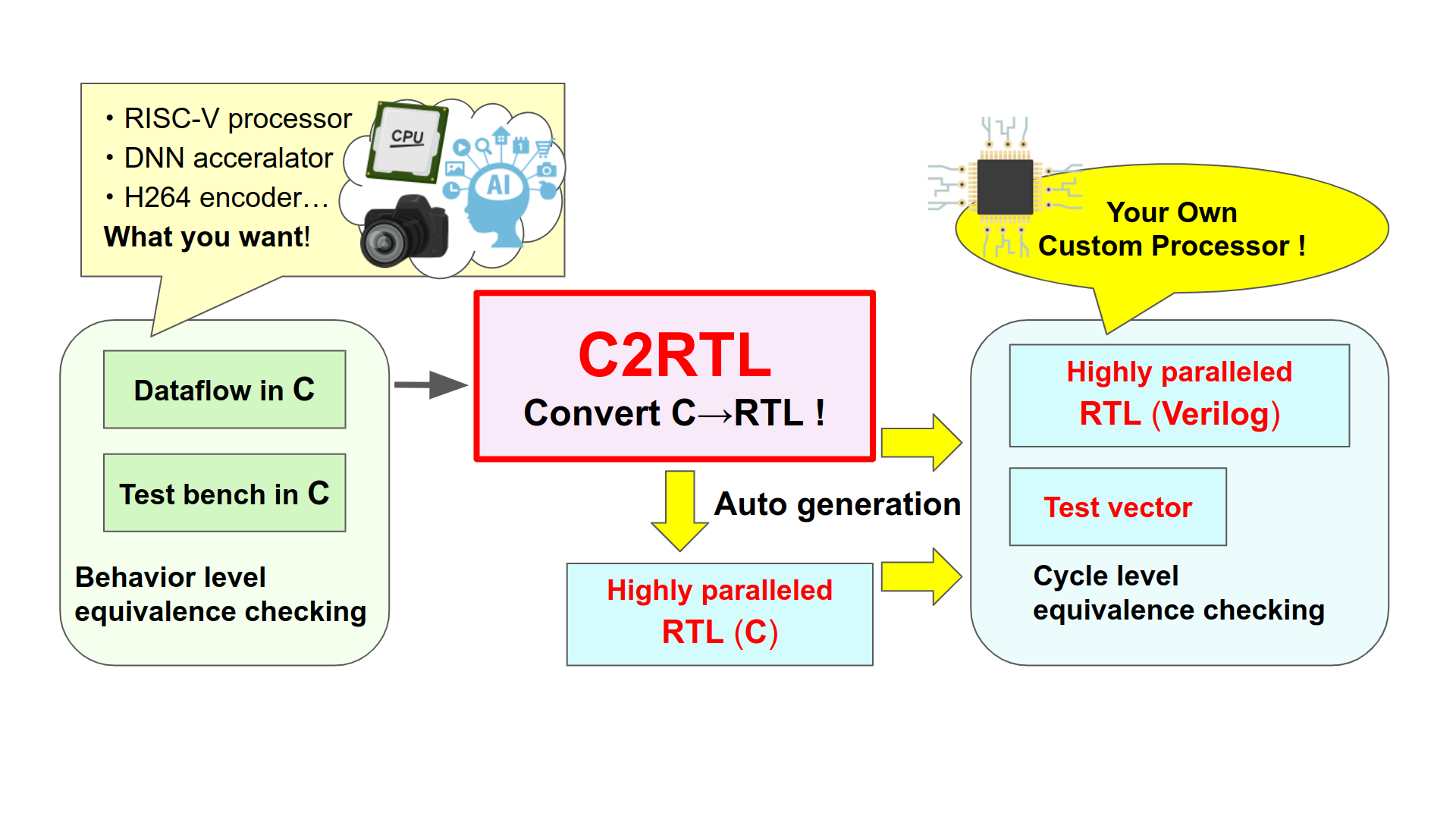

そこで本研究室ではC/C++でデータフローを記述したプロセッサをそのままHWのRTLに変換する「C2RTL」を開発しています.

C2RTLの主な特徴は次のような点です.

1. カスタムプロセッサのRTLを

C/C++プログラムのみで作製できる

2. サイクルレベル記述により設計者の意図通り動作し,深層学習などの超並列処理が簡単に表現・実装可能

3. SW環境でHWシミュレーションを行えるのでデバッグを効率・低コスト化

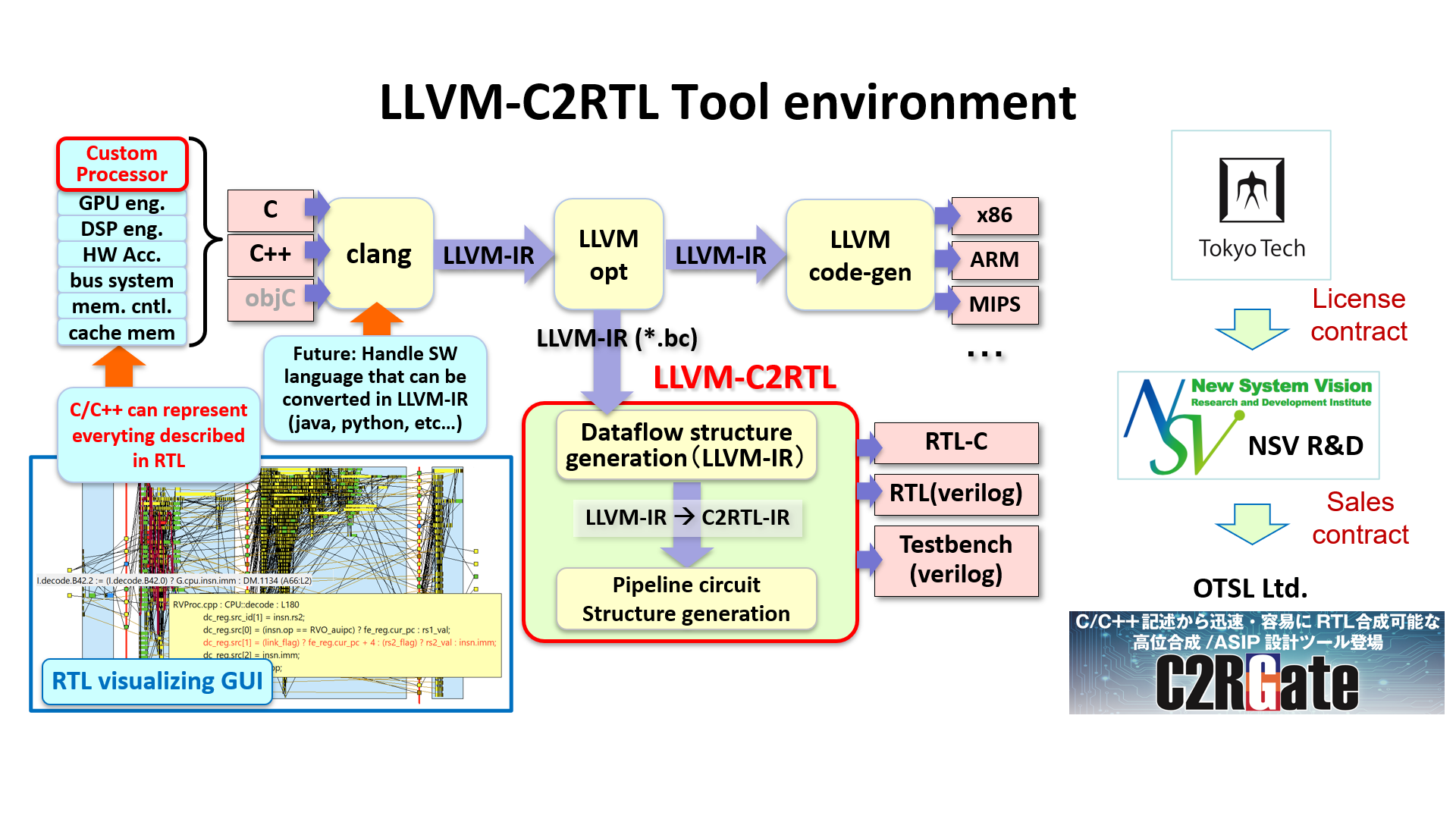

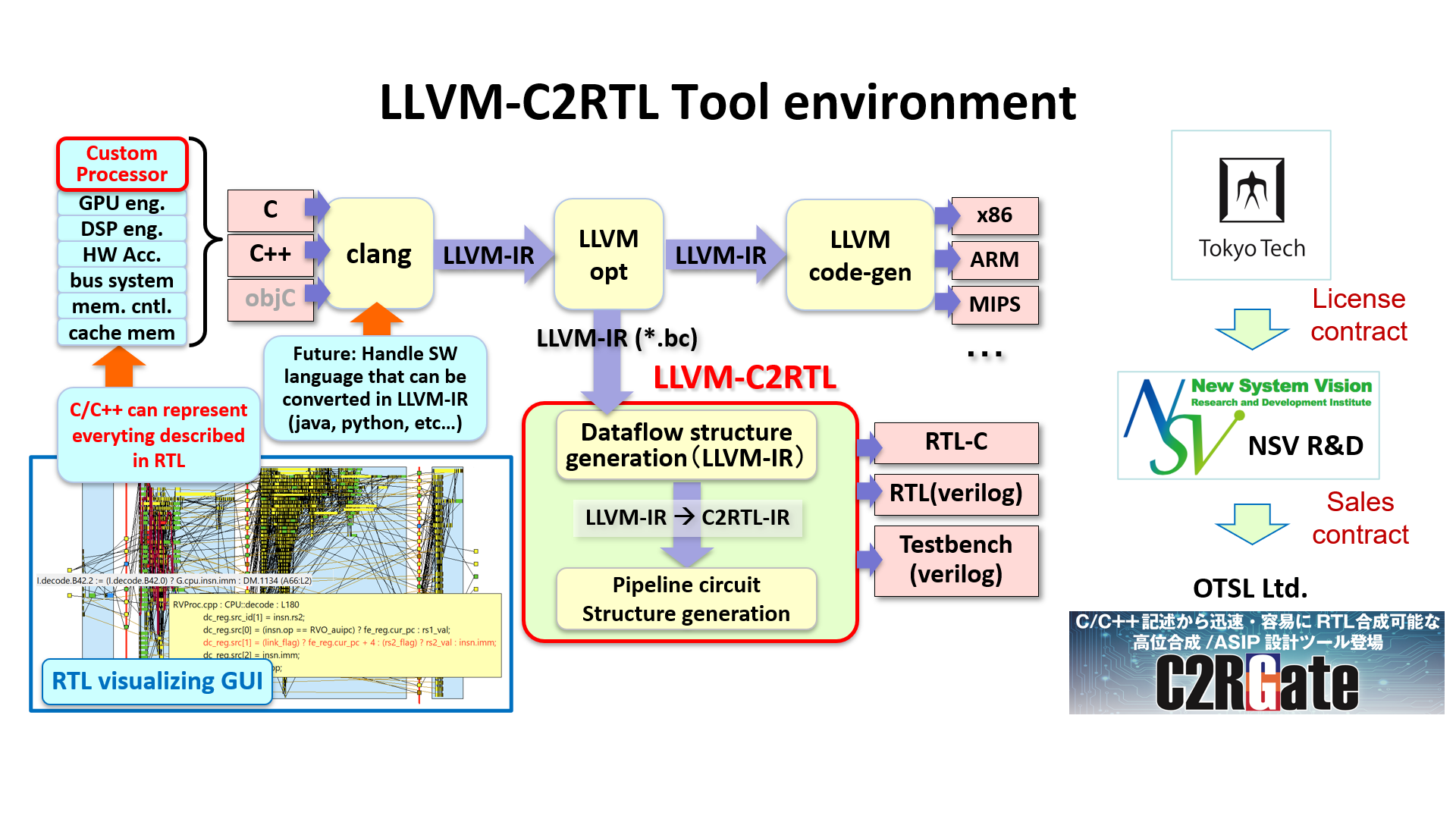

C2RTLは明示的なFSM(フィニットステートマシン)記述といった,RTLの抽象度と同じサイクルレベルの記述を行います.一般的な高位合成では記述スタイルや内部処理がツールごとに異なり,高品質なRTL作成のためにはツールへの習熟が不可欠です.C2RTLのサイクルレベルの記述ならSW~HWまで設計者の意図通り動作するため,ブラックボックスの無い,システムの内部まで把握した設計が可能です.

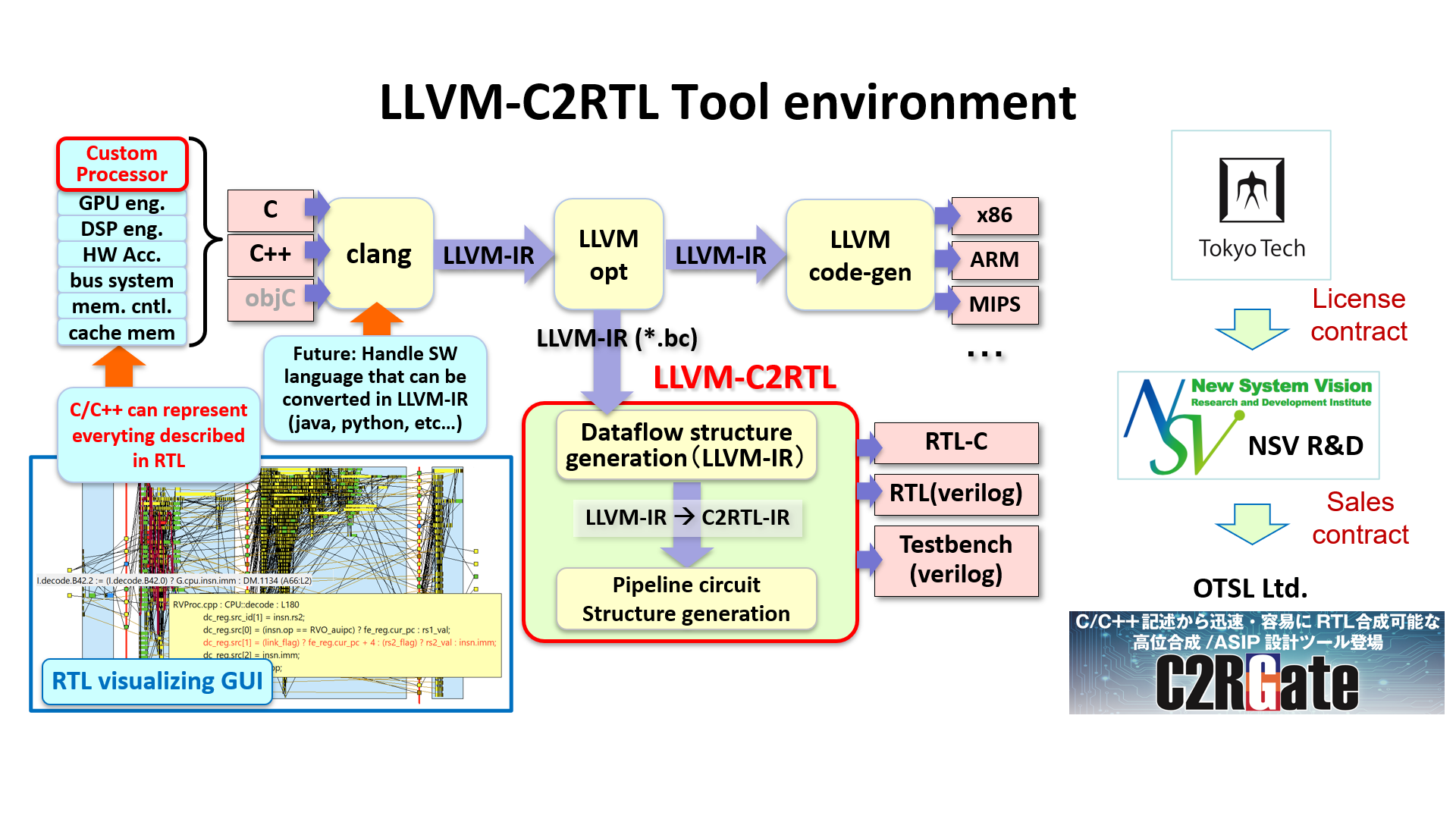

さらにC2RTLではLLVMを使用しており,RTLのみならずx86やArmなどの実行形式に変換することも出来ます.これによりC2RTL外の他の機能との高度な連携が可能になり,機能拡張や検証の幅が広がります.

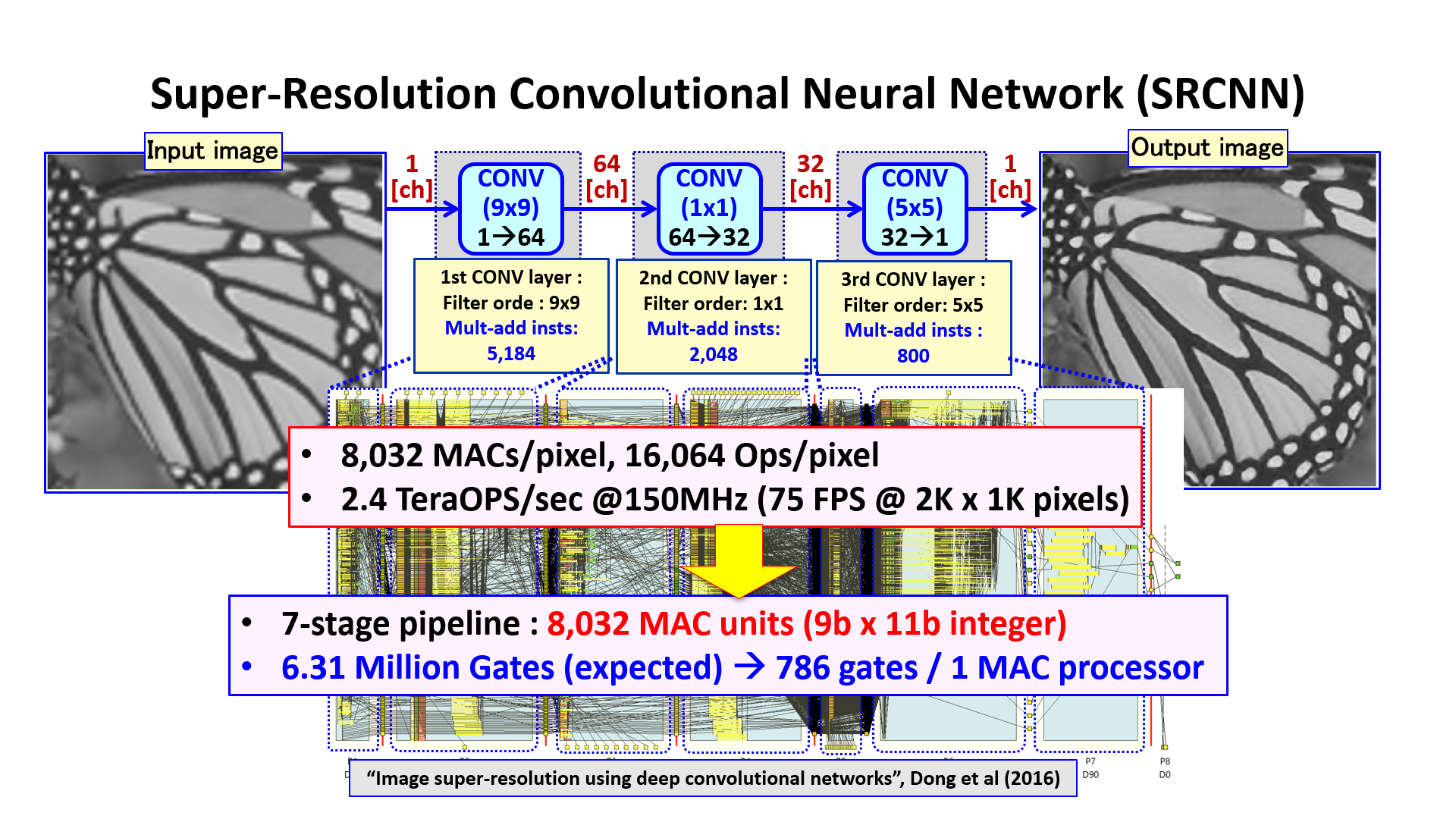

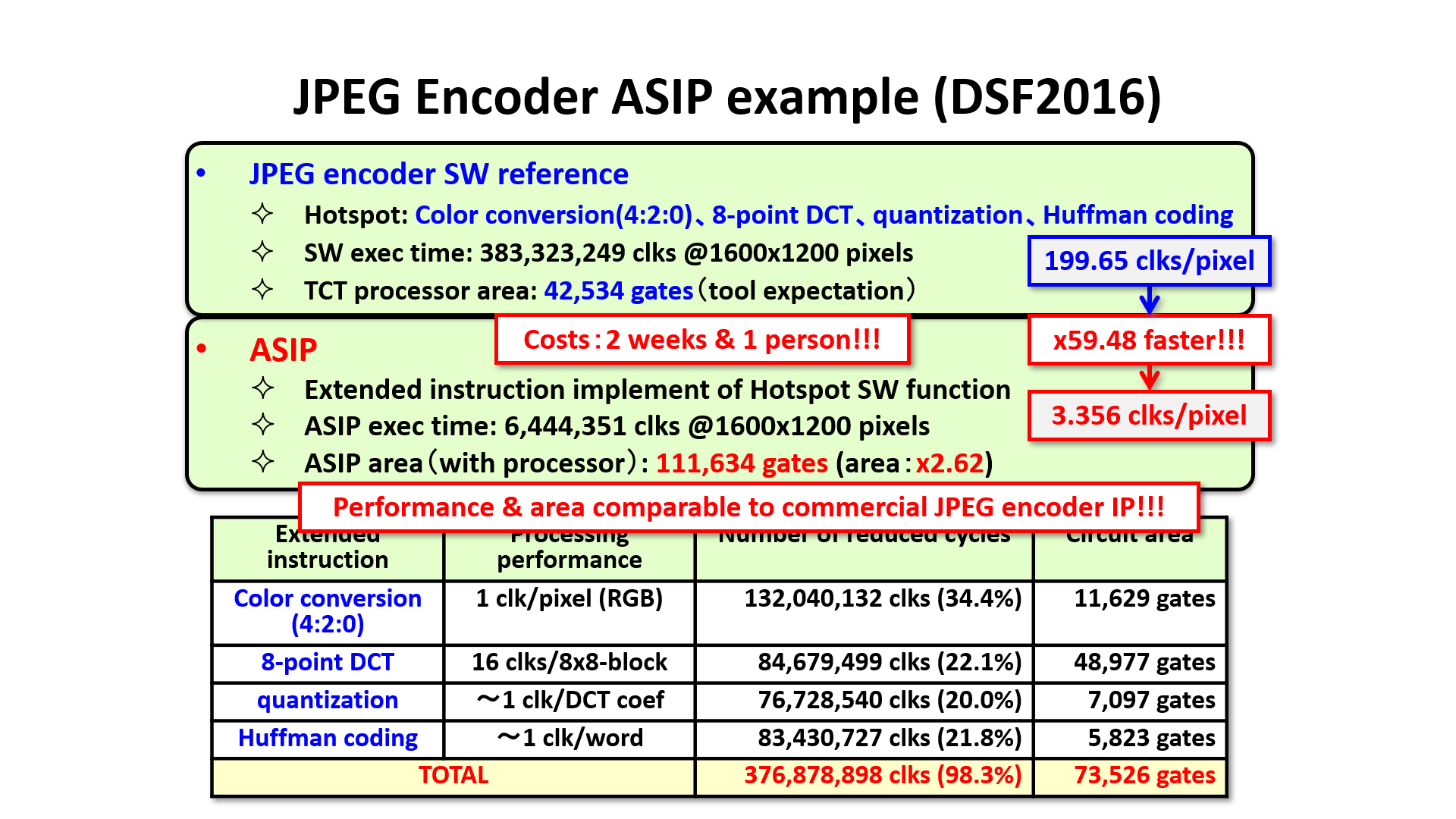

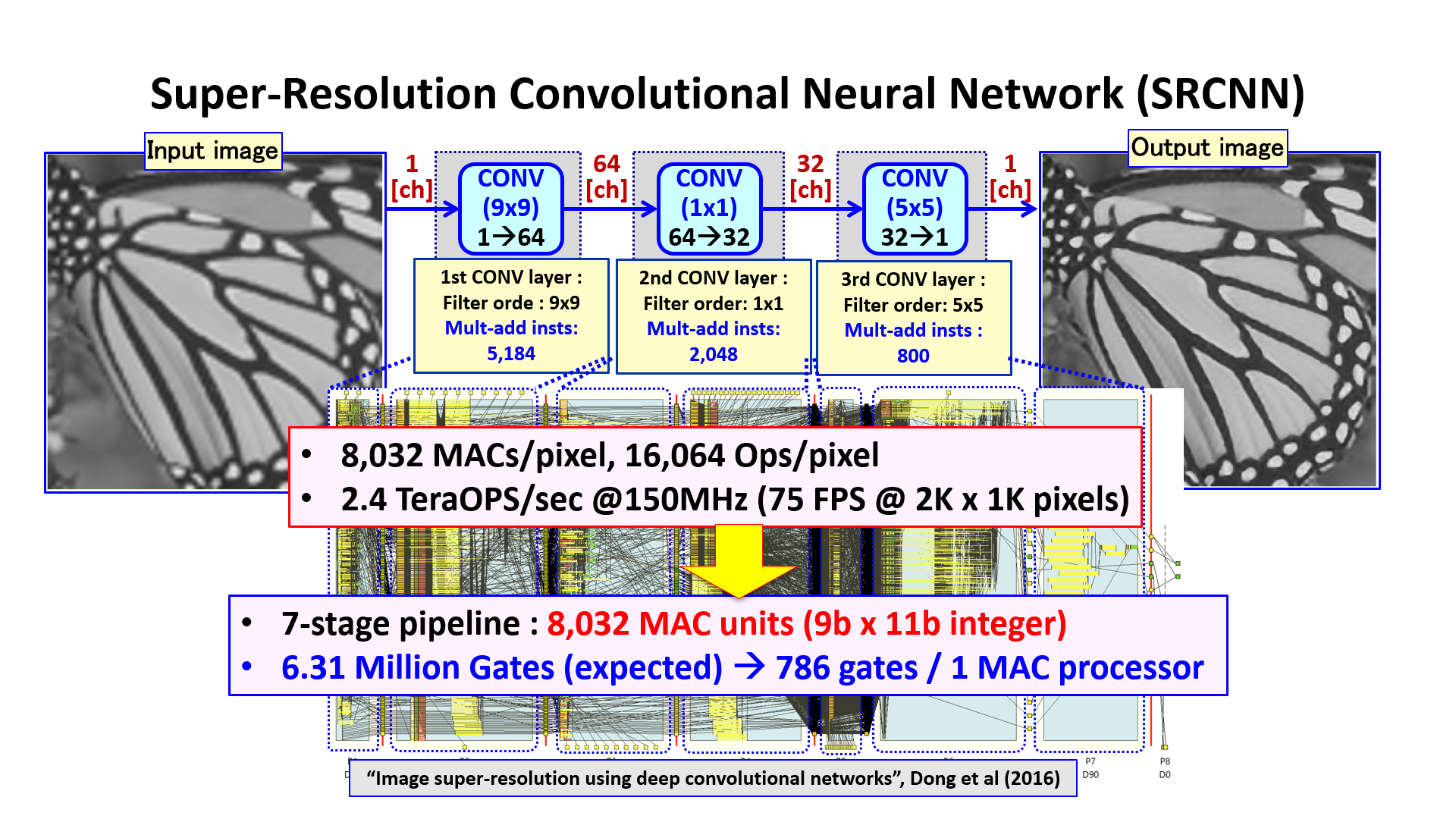

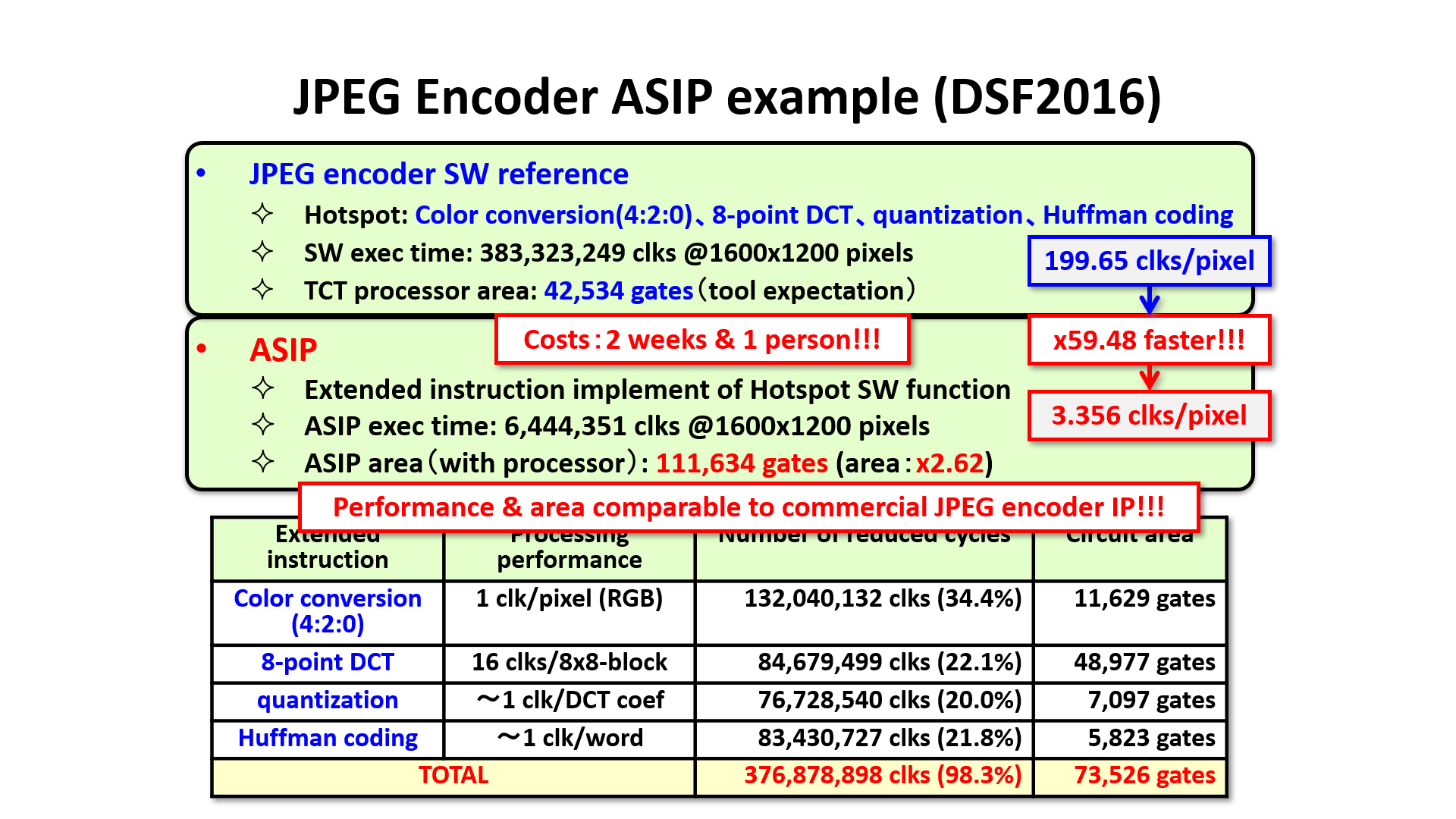

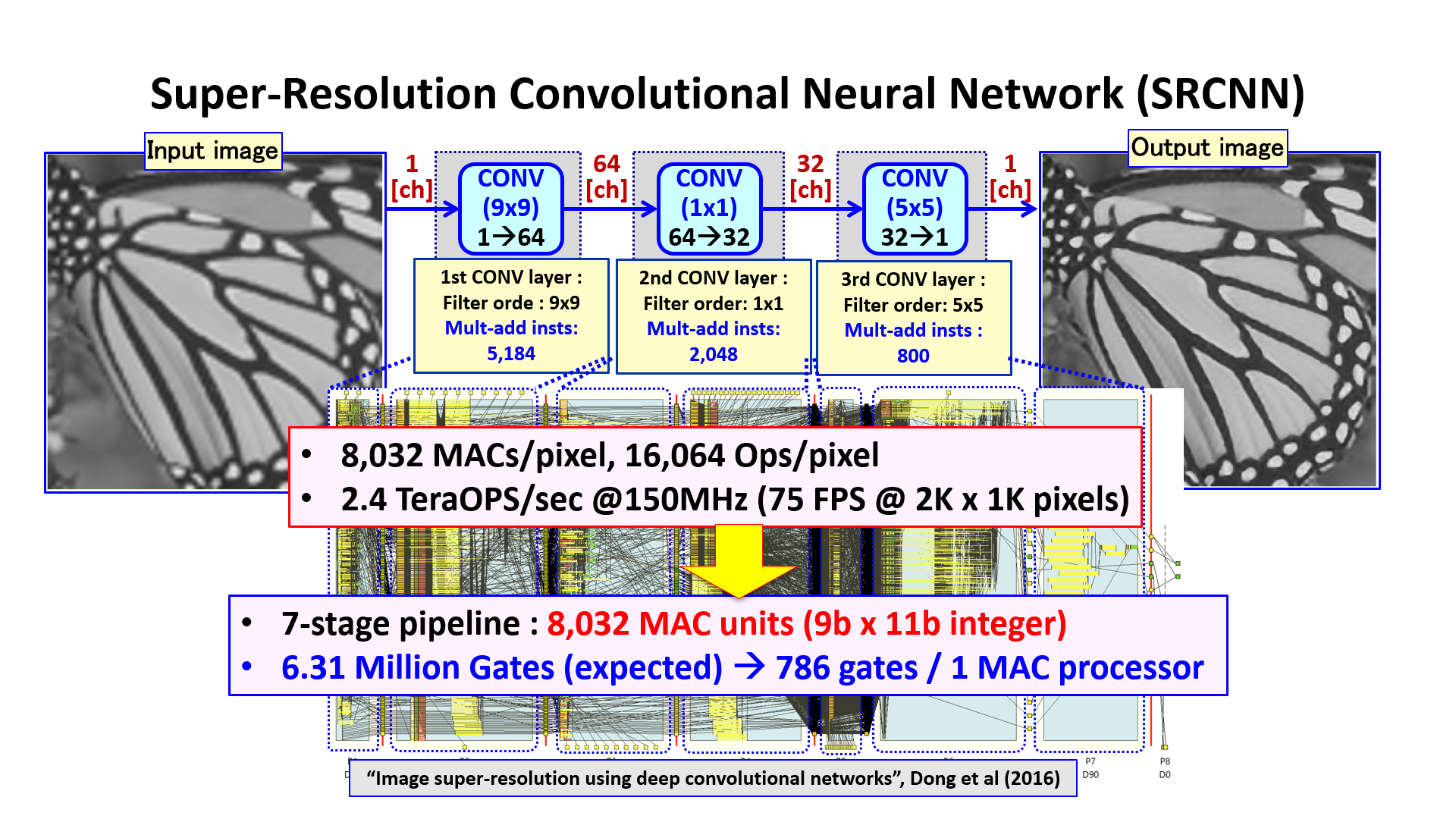

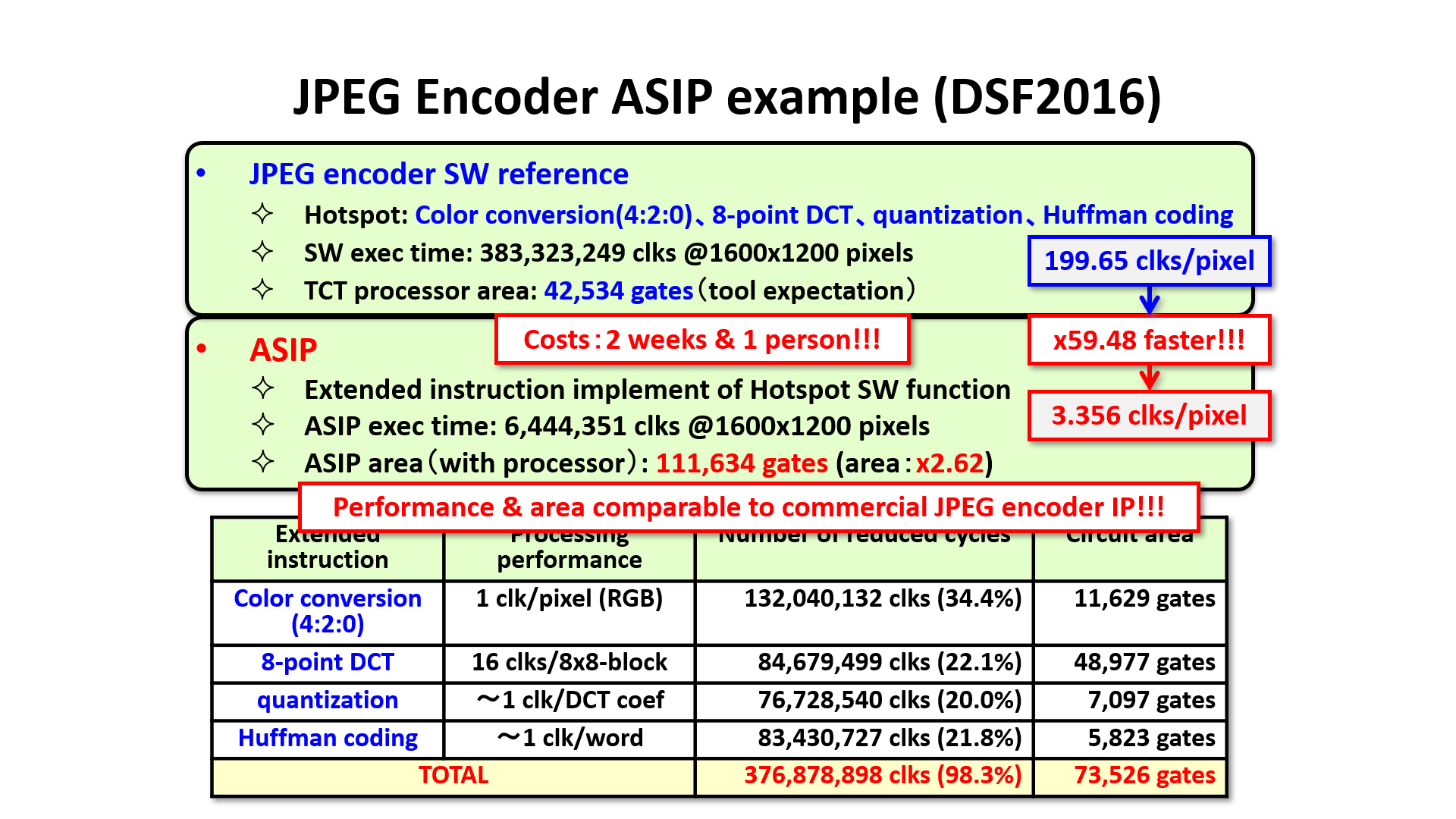

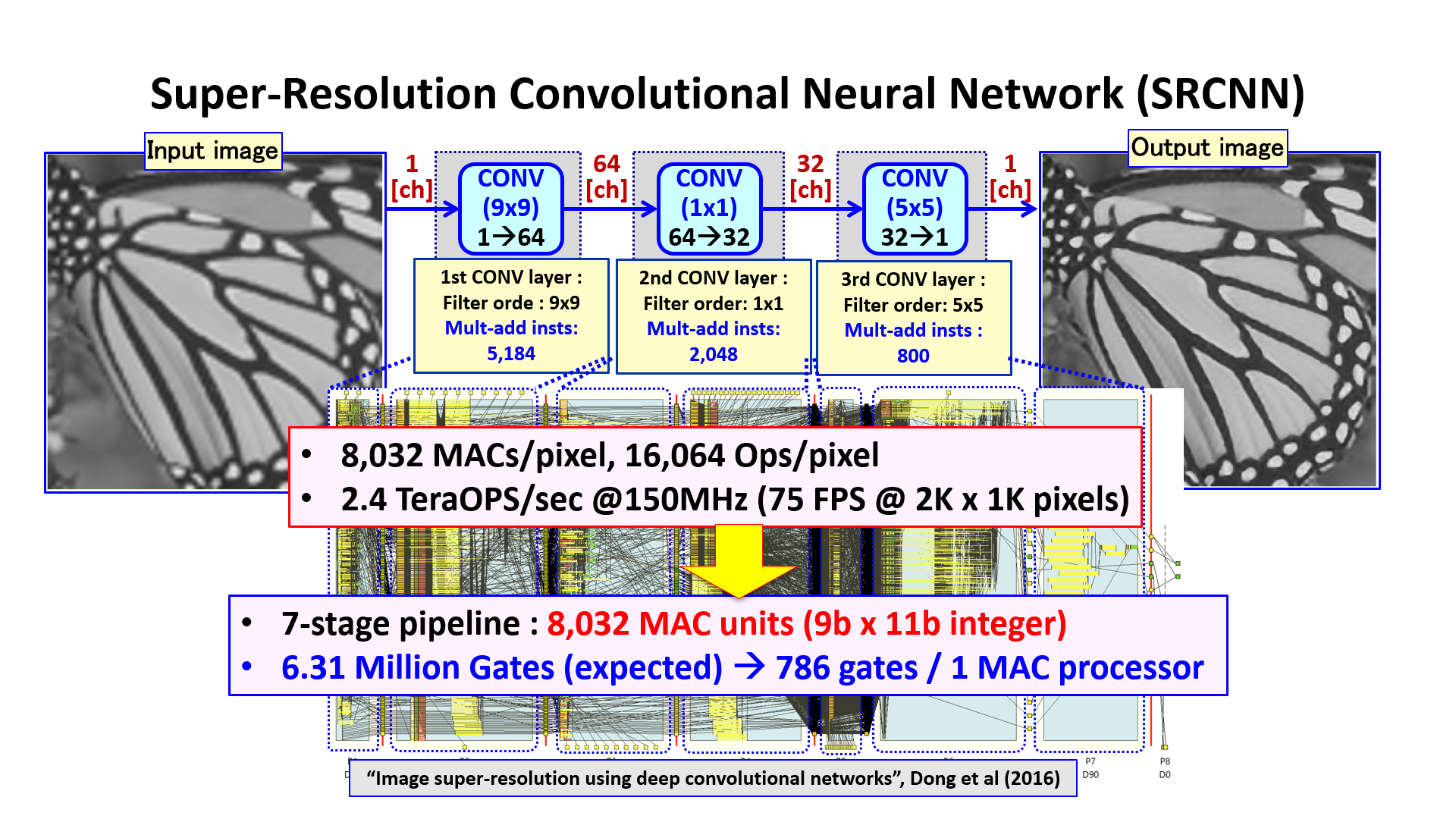

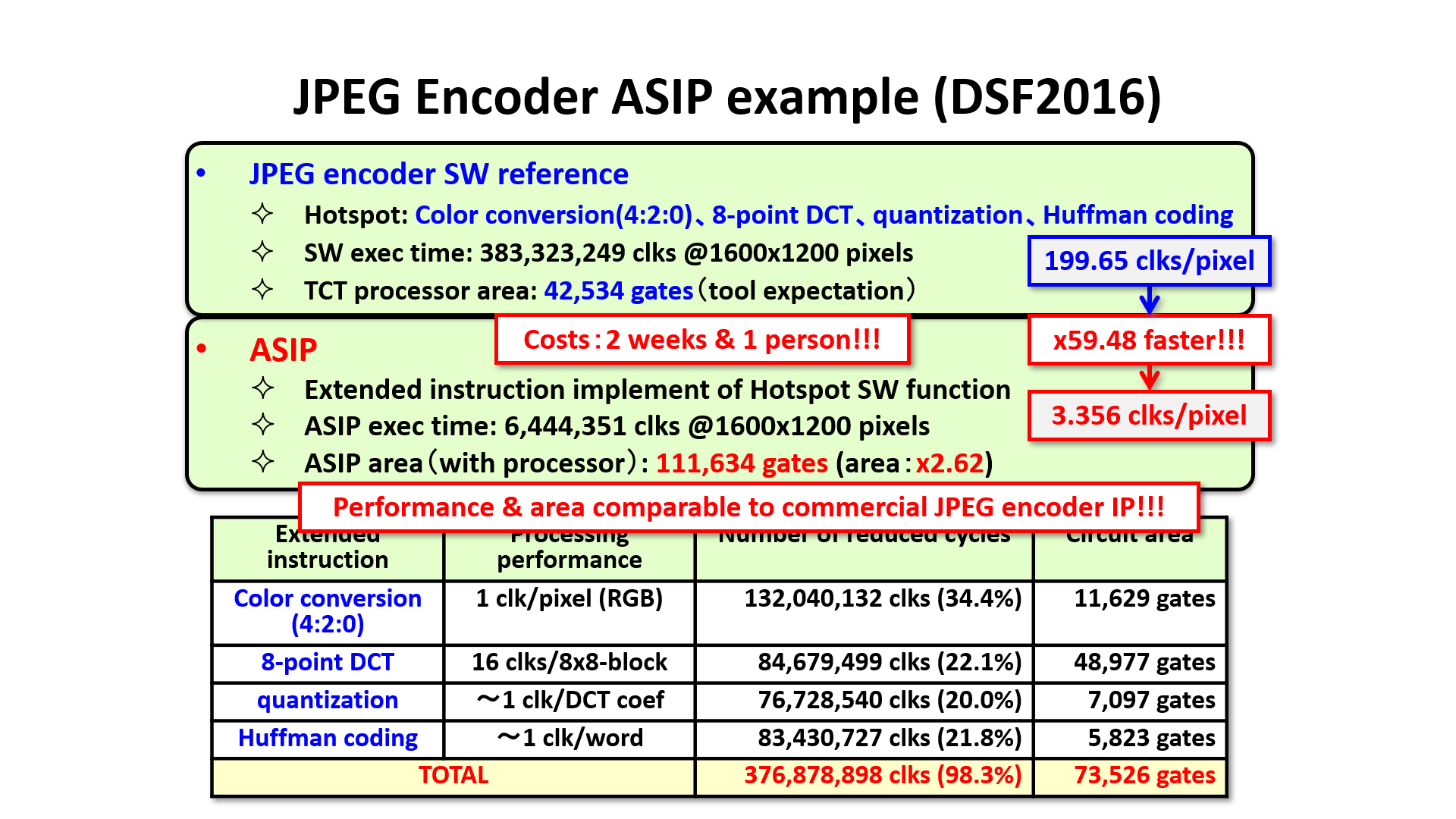

3層の畳み込みニューラルネットワークによる画像の超高解像度化において,C2RTLにより2ステージのパイプラインと8032個の積和演算器をもつプロセッサを作成し,150MHzの動作周波数で2.4TeraOPS/secの動作速度を達成しました.またJPEGエンコーダにおいては1人の人員でわずか2週間で商用IPに匹敵するエンコーダを作成できました.

当研究室ではこのようなHW/SW協調開発により指紋認証やDNNアクセラレータなどの実装にも取り組んでいます.

IoTやカスタムプロセッサの発展に対応して大きな注目を集めている技術に,誰でも無料で使え独自命令も実装できるオープンソースアーキテクチャであるRISC-Vがあります.

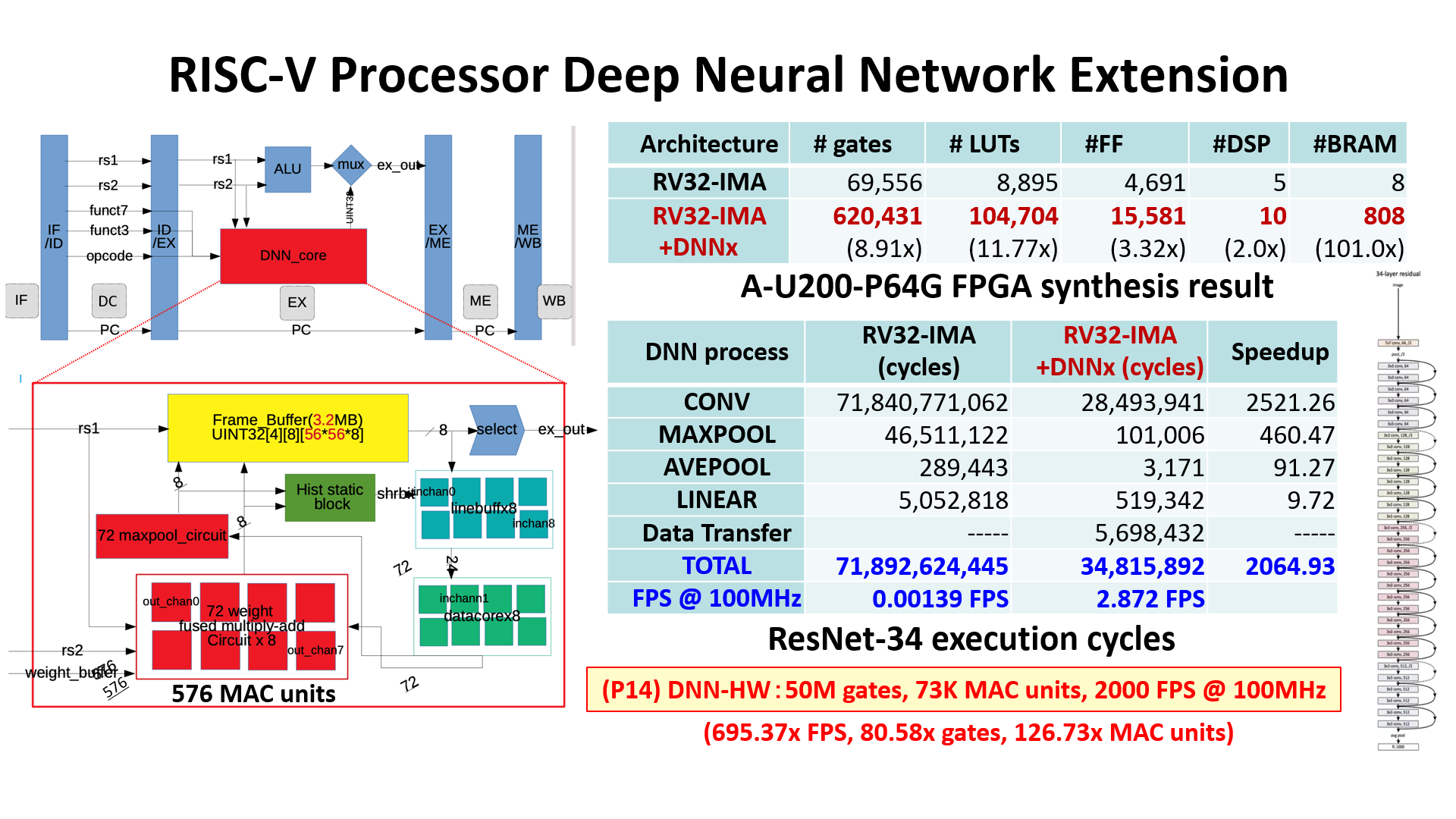

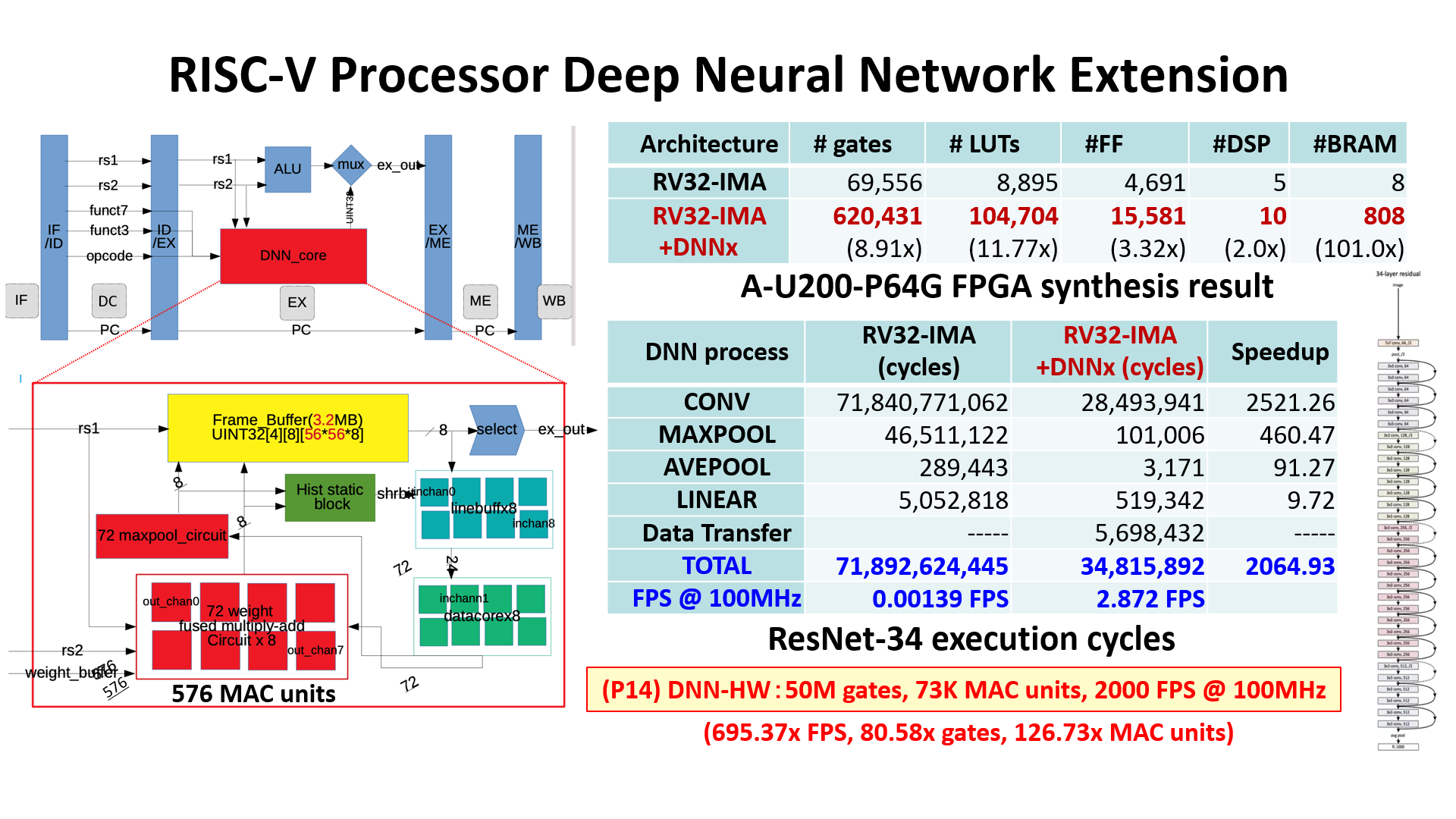

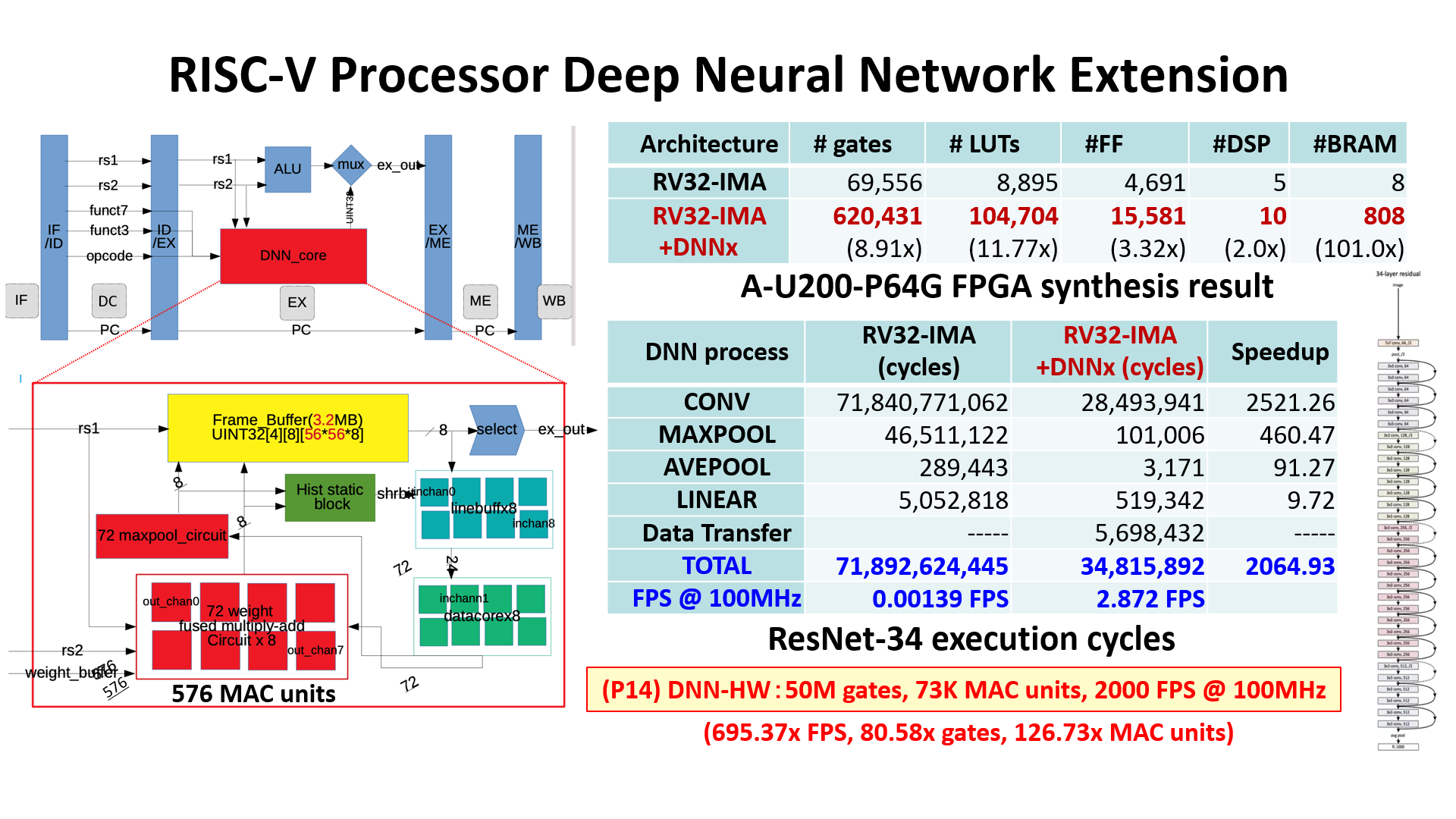

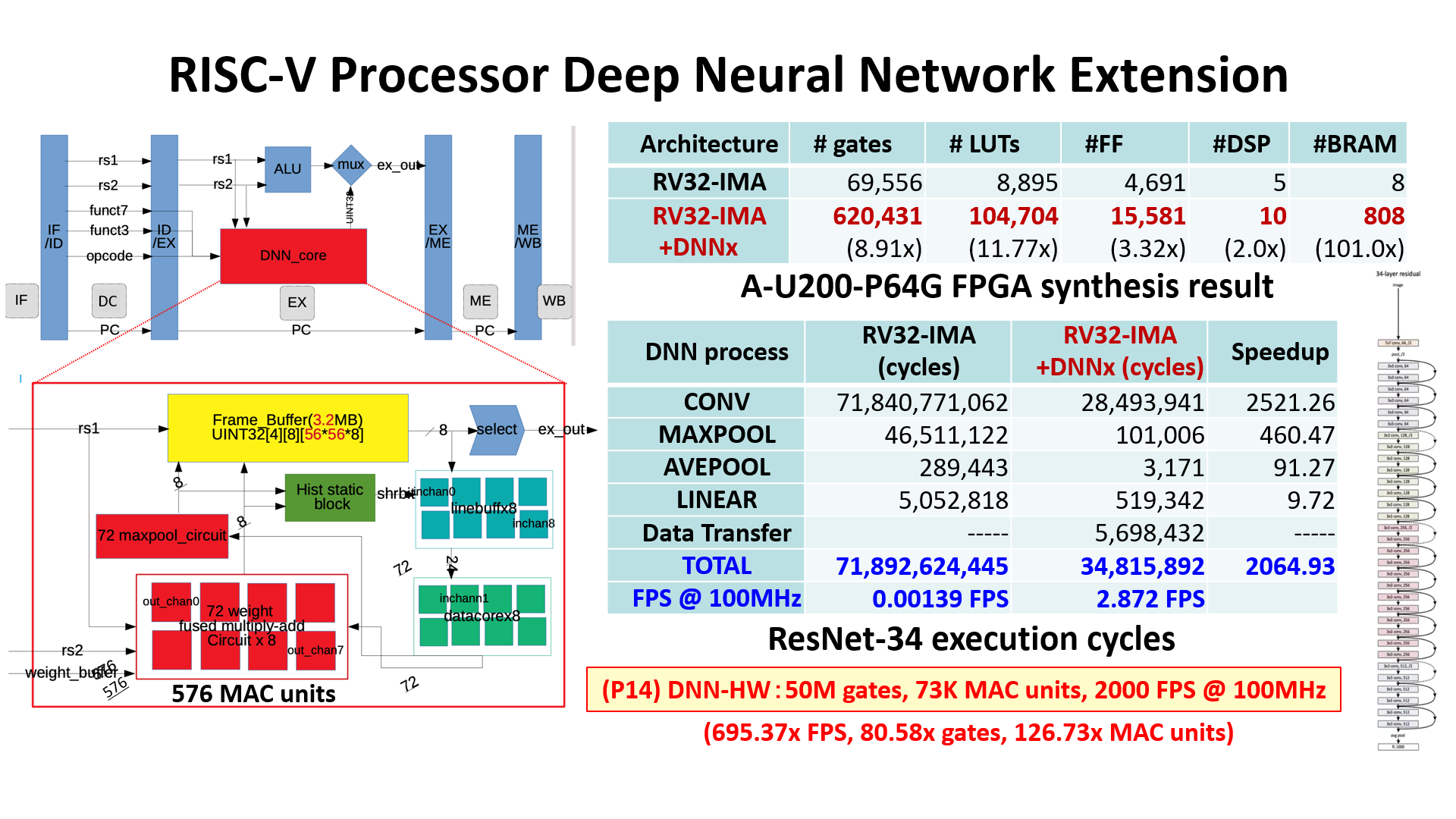

本研究室ではRISC-Vシステム設計プラットフォームとして,C2RTLを活用しながらより高度な機能をもったRISC-Vプロセッサの開発を行っています.RV32/64に対応し,MMU/キャッシュも実装されておりLinuxを動作させることができます.また演算機能としてFPU,DNNアクセラレータを備えおり,HW実装されたDNNアクセラレータは単純なSW実行に対して約700倍の高速化が行えます.

さらに現在はベクトルプロセッサや16bit圧縮命令,マルチコアとその検証環境の開発にも取り組んでいます.

AppleのM1チップやニューラルネットアクセラレータなど、大手IT企業をはじめ世界的に開発が進められているのが独自設計プロセッサや領域特化型プロセッサです.

ユーザの望む処理に最適化したハードウェアは高速かつ低消費電力性に非常に優れています.しかしその設計のためにはハードウェアに関する高度な知識・技術と,検証用に高いコストをかけハードウェアを試作する必要がありソフトウェア技術者のみでの開発は困難でした.

そこで本研究室ではC/C++でデータフローを記述したプロセッサをそのままHWのRTLに変換する「C2RTL」を開発しています.

C2RTLの主な特徴は次のような点です.

1. カスタムプロセッサのRTLを

C/C++プログラムのみで作製できる

2. サイクルレベル記述により設計者の意図通り動作し,深層学習などの超並列処理が簡単に表現・実装可能

3. SW環境でHWシミュレーションを行えるのでデバッグを効率・低コスト化

C2RTLは明示的なFSM(フィニットステートマシン)記述といった,RTLの抽象度と同じサイクルレベルの記述を行います.一般的な高位合成では記述スタイルや内部処理がツールごとに異なり,高品質なRTL作成のためにはツールへの習熟が不可欠です.C2RTLのサイクルレベルの記述ならSW~HWまで設計者の意図通り動作するため,ブラックボックスの無い,システムの内部まで把握した設計が可能です.

さらにC2RTLではLLVMを使用しており,RTLのみならずx86やArmなどの実行形式に変換することも出来ます.これによりC2RTL外の他の機能との高度な連携が可能になり,機能拡張や検証の幅が広がります.

3層の畳み込みニューラルネットワークによる画像の超高解像度化において,C2RTLにより2ステージのパイプラインと8032個の積和演算器をもつプロセッサを作成し,150MHzの動作周波数で2.4TeraOPS/secの動作速度を達成しました.またJPEGエンコーダにおいては1人の人員でわずか2週間で商用IPに匹敵するエンコーダを作成できました.

当研究室ではこのようなHW/SW協調開発により指紋認証やDNNアクセラレータなどの実装にも取り組んでいます.

IoTやカスタムプロセッサの発展に対応して大きな注目を集めている技術に,誰でも無料で使え独自命令も実装できるオープンソースアーキテクチャであるRISC-Vがあります.

本研究室ではRISC-Vシステム設計プラットフォームとして,C2RTLを活用しながらより高度な機能をもったRISC-Vプロセッサの開発を行っています.RV32/64に対応し,MMU/キャッシュも実装されておりLinuxを動作させることができます.また演算機能としてFPU,DNNアクセラレータを備えおり,HW実装されたDNNアクセラレータは単純なSW実行に対して約700倍の高速化が行えます.

さらに現在はベクトルプロセッサや16bit圧縮命令,マルチコアとその検証環境の開発にも取り組んでいます.

AppleのM1チップやニューラルネットアクセラレータなど、大手IT企業をはじめ世界的に開発が進められているのが独自設計プロセッサや領域特化型プロセッサです.

ユーザの望む処理に最適化したハードウェアは高速かつ低消費電力性に非常に優れています.しかしその設計のためにはハードウェアに関する高度な知識・技術と,検証用に高いコストをかけハードウェアを試作する必要がありソフトウェア技術者のみでの開発は困難でした.

そこで本研究室ではC/C++でデータフローを記述したプロセッサをそのままHWのRTLに変換する「C2RTL」を開発しています.

C2RTLの主な特徴は次のような点です.

1. カスタムプロセッサのRTLを

C/C++プログラムのみで作製できる

2. サイクルレベル記述により設計者の意図通り動作し,深層学習などの超並列処理が簡単に表現・実装可能

3. SW環境でHWシミュレーションを行えるのでデバッグを効率・低コスト化

C2RTLは明示的なFSM(フィニットステートマシン)記述といった,RTLの抽象度と同じサイクルレベルの記述を行います.一般的な高位合成では記述スタイルや内部処理がツールごとに異なり,高品質なRTL作成のためにはツールへの習熟が不可欠です.C2RTLのサイクルレベルの記述ならSW~HWまで設計者の意図通り動作するため,ブラックボックスの無い,システムの内部まで把握した設計が可能です.

さらにC2RTLではLLVMを使用しており,RTLのみならずx86やArmなどの実行形式に変換することも出来ます.これによりC2RTL外の他の機能との高度な連携が可能になり,機能拡張や検証の幅が広がります.

3層の畳み込みニューラルネットワークによる画像の超高解像度化において,C2RTLにより2ステージのパイプラインと8032個の積和演算器をもつプロセッサを作成し,150MHzの動作周波数で2.4TeraOPS/secの動作速度を達成しました.またJPEGエンコーダにおいては1人の人員でわずか2週間で商用IPに匹敵するエンコーダを作成できました.

当研究室ではこのようなHW/SW協調開発により指紋認証やDNNアクセラレータなどの実装にも取り組んでいます.

IoTやカスタムプロセッサの発展に対応して大きな注目を集めている技術に,誰でも無料で使え独自命令も実装できるオープンソースアーキテクチャであるRISC-Vがあります.

本研究室ではRISC-Vシステム設計プラットフォームとして,C2RTLを活用しながらより高度な機能をもったRISC-Vプロセッサの開発を行っています.RV32/64に対応し,MMU/キャッシュも実装されておりLinuxを動作させることができます.また演算機能としてFPU,DNNアクセラレータを備えおり,HW実装されたDNNアクセラレータは単純なSW実行に対して約700倍の高速化が行えます.

さらに現在はベクトルプロセッサや16bit圧縮命令,マルチコアとその検証環境の開発にも取り組んでいます.

AppleのM1チップやニューラルネットアクセラレータなど、大手IT企業をはじめ世界的に開発が進められているのが独自設計プロセッサや領域特化型プロセッサです.

ユーザの望む処理に最適化したハードウェアは高速かつ低消費電力性に非常に優れています.しかしその設計のためにはハードウェアに関する高度な知識・技術と,検証用に高いコストをかけハードウェアを試作する必要がありソフトウェア技術者のみでの開発は困難でした.

そこで本研究室ではC/C++でデータフローを記述したプロセッサをそのままHWのRTLに変換する「C2RTL」を開発しています.

C2RTLの主な特徴は次のような点です.

1. カスタムプロセッサのRTLを

C/C++プログラムのみで作製できる

2. サイクルレベル記述により設計者の意図通り動作し,深層学習などの超並列処理が簡単に表現・実装可能

3. SW環境でHWシミュレーションを行えるのでデバッグを効率・低コスト化

C2RTLは明示的なFSM(フィニットステートマシン)記述といった,RTLの抽象度と同じサイクルレベルの記述を行います.一般的な高位合成では記述スタイルや内部処理がツールごとに異なり,高品質なRTL作成のためにはツールへの習熟が不可欠です.C2RTLのサイクルレベルの記述ならSW~HWまで設計者の意図通り動作するため,ブラックボックスの無い,システムの内部まで把握した設計が可能です.

さらにC2RTLではLLVMを使用しており,RTLのみならずx86やArmなどの実行形式に変換することも出来ます.これによりC2RTL外の他の機能との高度な連携が可能になり,機能拡張や検証の幅が広がります.

3層の畳み込みニューラルネットワークによる画像の超高解像度化において,C2RTLにより2ステージのパイプラインと8032個の積和演算器をもつプロセッサを作成し,150MHzの動作周波数で2.4TeraOPS/secの動作速度を達成しました.またJPEGエンコーダにおいては1人の人員でわずか2週間で商用IPに匹敵するエンコーダを作成できました.

当研究室ではこのようなHW/SW協調開発により指紋認証やDNNアクセラレータなどの実装にも取り組んでいます.

IoTやカスタムプロセッサの発展に対応して大きな注目を集めている技術に,誰でも無料で使え独自命令も実装できるオープンソースアーキテクチャであるRISC-Vがあります.

本研究室ではRISC-Vシステム設計プラットフォームとして,C2RTLを活用しながらより高度な機能をもったRISC-Vプロセッサの開発を行っています.RV32/64に対応し,MMU/キャッシュも実装されておりLinuxを動作させることができます.また演算機能としてFPU,DNNアクセラレータを備えおり,HW実装されたDNNアクセラレータは単純なSW実行に対して約700倍の高速化が行えます.

さらに現在はベクトルプロセッサや16bit圧縮命令,マルチコアとその検証環境の開発にも取り組んでいます.

created with

Website Builder Software .